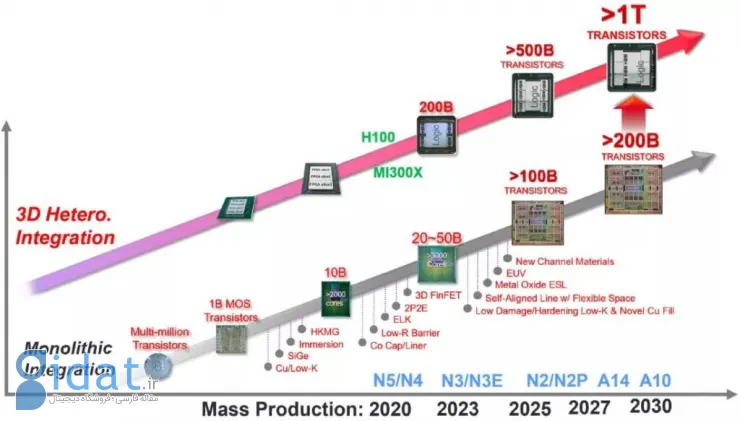

انتظار میرود TSMC با فرایندهای جدید بهسمت تولید تراشههایی با معماری سهبعدی برای میزبانی از یک تریلیون ترانزیستور برود.

در کنفرانس اخیر IEDM، شرکت تایوانی TSMC از نقشه راه نیمهرساناها و گرههای (Nodes) تولید نسل بعدی تراشههای خود رونمایی کرد. در این کنفرانس از نوعی معماری انباشتهسازی سهبعدی مبتنی بر چیپلت پرده برداشته شد که میتوان با آن یک تریلیون ترانزیستور را در یک تراشه گنجاند. انتظار میرود که این تراشه در سال 2030 رونمایی شود.

براساس گزارش TechSpot، شرکت TSMC برای رسیدن به یک تریلیون ترانزیستور در یک تراشه، از فناوریهای بستهبندی مانند CoWoS ،InFO و SoIC استفاده خواهد کرد. این شرکت همچنین انتظار دارد که با این فناوریها تا سال 2030 معماری مونولیتیک خود را به 200 میلیارد ترانزیستور برساند.

درحالحاضر TSMC درحال توسعه گرههای تولید N2 و N2P کلاس 2 نانومتری و فرایندهای ساخت A14 کلاس 1.4 نانومتری و A10 کلاس 1 نانومتری است. این شرکت انتظار دارد تا پایان سال 2025، تولید 2 نانومتری خود را آغاز کند. تایوانیها در سال 2028 نیز بهسمت فرایند 1.4 نانومتری A14 حرکت خواهند کرد و احتمالاً تا سال 2030 ترانزیستورهای 1 نانومتری تولید میکنند.

تراشه انویدیا GH100 با 80 میلیارد ترانزیستور یکی از پیچیدهترین پردازندههای یکپارچه موجود در بازار است. بااینحال، اندازه این پردازندهها بزرگتر و البته گرانتر است. ازاینرو، TSMC معتقد است که تولیدکنندگان از معماریهای چندچیپلتی همانند معماری تراشه Instinct MI300X از AMD که اخیراً عرضه شده یا Ponte Vecchio اینتل که دارای 100 میلیارد ترانزیستور است، استفاده خواهند کرد.

درهمینحال، اینتل روی فرایند 2 نانومتری (20 آمپر) و 1.8 نانومتری (18 آمپر) خود کار میکند. یکی از مزیتهای این فناوری جدید، سیستمی برای انتقال انرژی از پشت (Backside) به نام PowerVia است که میتواند چگالی بالاتر، سرعت کلاک بیشتر و مصرف انرژی کمتر را فراهم کند. «پت گلسینگر»، مدیرعامل اینتل، ادعا کرده است که گره پردازشی 18A آنها نسبت به تراشههای 2 نانومتری TSMC عملکرد بهتری خواهد داشت.

برای مقایسه عملکرد این دو غول تراشهسازی باید تا نیمه دوم سال 2024 منتظر ماند. TSMC احتمالاً تا آن زمان N3P را در کنار محصولات 20A و 18A خود به تولید انبوه میرساند.

پاسخ ها